本文設計了基于TMS320C6000系列DSP的MPEG-4編碼器。將攝像頭獲取的圖像以MPEG-4標準進行實時壓縮并通過VGA實時顯示,同時把壓縮好的數據通過PCI總線傳輸給ARM控制器,經由ARM根據實際的需要進行視頻數據的網絡傳輸。

MPEG-4 是一種開放性標準,其中許多部分都沒有規定,可以加入一些新的算法,因此采用通用DSP能夠隨時更新算法、優化算法,使得編碼效率更高。由于MPEG-4 編碼算法復雜,需要存儲的數據量大,無論是存儲空間分配、數據傳輸還是運算速度對DSP來說都是挑戰。

C6000系列DSP是TI公司生產的高檔DSP。這一系列DSP都是基VelociTITM構架的VLIW DSP,它在每個周期可以執行八條32bit 的指令, 具有高達200MHZ的CPU,從而使得其運算能力達到1600MIPS。而6416在600MHz主頻下,只利用50%的運算能力就可以同時進行單通道MPEG-4視頻編碼、單通道MPEG-4視頻解碼和單通道MPEG-2視頻編碼的處理。同時其對外接口靈活、開發工具齊全,被大多數嵌入式圖像實時壓縮系統所采用。因此本系統采用TI公司TMS320C6416芯片為核心處理器。

1.TMS320C6416的結構及特點

DSP的CPU結構如圖1所示,它具有兩個通道,每個通道具有4個功能單元(1個乘法器和3個算術邏輯單元),16個32位通用寄存器,每個通道的功能單元可以隨意訪問本通道的寄存器。CPU還有兩個交叉單元,通過它們,一個通道的功能單元可以訪問另一個通道的寄存器。另外, CPU還具有256 bit寬的數據和程序通道,可以使程序存儲器在每個時鐘周期提供8條并行執行指令。這種CPU結構是DSP具有VLIW結構的最基本條件。此DSP的存儲空間映射為內部存儲器、內部外設及擴展存儲器。其中內部存儲器由64KB內部程序存儲器和數據存儲器構成,內部程序存儲器可以映射到CPU地址空間或者作為Cache操作。內部和外部數據存儲器均可通過CPU、DMA或HPI(Host Interface)方式訪問,HPI接口使上位機可以訪問DSP的存儲空間。2.系統硬件設計

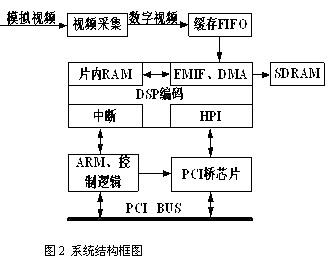

本系統主要分為三部分,分別是視頻采集模塊、視頻的MPEG-4編碼模塊和視頻傳輸模塊,其結構框圖如圖2所示。