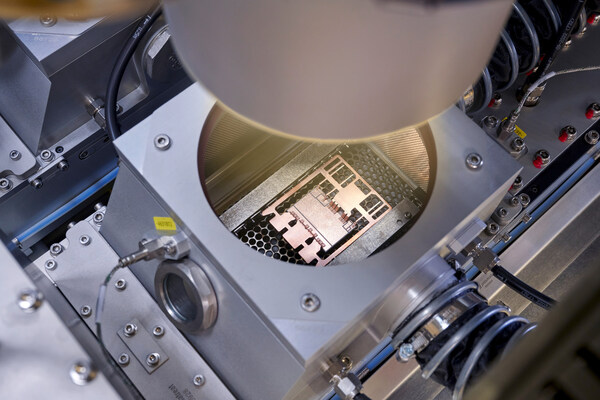

加利福尼亞州圣克拉拉2023年9月28日 /美通社/ -- AMD(超威,納斯達克股票代碼:AMD)今日宣布推出 AMD Alveo? UL3524 加速卡,這是一款面向超低時延電子交易應用設計的新款金融科技( fintech )加速卡。Alveo UL3524 已由領先的交易公司進行了部署,并且支持多種解決方案合作伙伴產(chǎn)品,能夠為自營交易商、做市商、對沖基金、經(jīng)紀商和交易所提供一流的 FPGA 平臺,以納秒( ns )速度進行電子交易。

較之上一代 FPGA 技術,Alveo UL3524 帶來了 7 倍的時延提升[1],從而達到小于 3 納秒的 FPGA 收發(fā)器時延[2],加速交易執(zhí)行。其由定制的 16nm Virtex? UltraScale?+ FPGA 提供支持,采用新穎的收發(fā)器架構,其具備硬化且經(jīng)過優(yōu)化的網(wǎng)絡連接核,以實現(xiàn)突破性能。通過在量產(chǎn)平臺上將硬件靈活性與超低時延網(wǎng)絡相結合,Alveo UL3524 能夠比傳統(tǒng) FPGA 替代方案更快實現(xiàn)設計收斂與部署。

AMD 產(chǎn)品營銷總監(jiān) Hamid Salehi 表示:"在超低時延交易中,1 納秒即可決定交易的盈虧。Alveo UL3524 加速卡由 AMD 超低時延 FPGA 收發(fā)器提供支持,專為給我們身處金融市場的金融科技客戶帶來可觀的競爭優(yōu)勢而打造。"

硬件靈活性以及人工智能賦能的交易策略

Alveo UL3254 采用 64 個超低時延收發(fā)器、78 萬個 FPGA 架構查找表( LUT )以及 1,680 個數(shù)字信號處理( DSP )計算片,旨在加速硬件中的定制交易算法,令交易商能夠根據(jù)不斷演進的策略和市場條件定制其設計。該產(chǎn)品為采用 Vivado? 設計套件的傳統(tǒng) FPGA 流程所支持,配套提供一套參考設計和性能基準,使 FPGA 設計人員能夠快速探索關鍵指標并根據(jù)規(guī)范開發(fā)定制交易策略,并得到 AMD 領域專家的全球支持。

為了簡化人工智能( AI )在算法交易市場中日益普遍的采用,AMD 為開發(fā)人員提供了開源且受到社區(qū)支持的FINN 開發(fā)框架。通過使用 PyTorch 和神經(jīng)網(wǎng)絡量化技術,F(xiàn)INN 項目令開發(fā)人員能夠在縮小 AI 模型尺寸的同時保持準確性、編譯到硬件 IP 以及將網(wǎng)絡模型集成到算法的數(shù)據(jù)路徑中,帶來低時延性能。作為一項開源計劃,該解決方案為開發(fā)人員賦予了靈活性與可及性可,可隨項目演進獲取最新技術進展。

實現(xiàn)不斷壯大的超低時延金融科技解決方案生態(tài)系統(tǒng)

Alveo UL3524 及專屬打造的 FPGA 技術使戰(zhàn)略合作伙伴能夠為金融科技市場構建定制解決方案和基礎設施。目前可供使用的合作伙伴解決方案包括來自 Alpha Data、Exegy 和 Hypertec 的產(chǎn)品。

為 Alveo UL3524 加速卡提供支持的 AMD Virtex? UltraScale+ VU2P FPGA 使 Alpha Data 的超低時延設備成為可能。

Alpha Data 總經(jīng)理 David Miller 表示:"AMD 的新款 Virtex UltraScale+ FPGA 為超低時延交易和網(wǎng)絡帶來了跨越式改進。我們開發(fā)的 ADA-R9100 機架式設備使客戶能夠輕松地充分發(fā)揮全新 AMD FPGA 器件的全部潛力。"

Exegy 作為端到端前臺交易解決方案提供商,正在利用其 nxFramework 為 Alveo UL3524 卡提供支持。nxFramework 是一種軟件與硬件開發(fā)環(huán)境,專為在金融行業(yè)內創(chuàng)建和維護超低時延 FPGA 應用定制而成。

Exegy FPGA 解決方案總監(jiān) Olivier Cousin 表示:"通過結合 AMD 開創(chuàng)性的超低時延 FPGA 技術與 Exegy 在資本市場的專長,我們得以提供一款綜合全面的解決方案,應對構建未來交易基礎設施所需面臨的日益增多的優(yōu)化問題。"

針對 Alveo UL3524,Hypertec 借助定制冷卻系統(tǒng)優(yōu)化了其 ORION HF X410R-G6 高頻服務器,使之部署在 1U 服務器尺寸規(guī)格中。

Hypertec 產(chǎn)品營銷總監(jiān) David Lim 表示:"Hypertec 工程師專門設計了 HF X410R-G6,以充分施展 Alveo UL3524 平臺的功能和速度,使我們的解決方案能夠滿足低時延任務極其嚴苛的需求。"

AMD Alveo UL3524 加速卡目前已投入量產(chǎn),并向全球金融服務客戶供貨。

相關資源

關于AMD

在超過五十年的歷史中,AMD(超威半導體)引領了高性能運算、圖形,以及可視化技術方面的創(chuàng)新。全球數(shù)十億計的人們、領先的 500 強公司,以及尖端科學研究所都依靠 AMD 技術來改善他們的生活、工作以及娛樂。AMD 員工致力于打造領先的高性能和自適應產(chǎn)品,努力拓寬技術的極限。成就今日,啟迪未來。更多信息,敬請訪問 AMD 公司(NASDAQ:AMD)-官網(wǎng) http://www.amd.com.cn/,關注 AMD 官方微信:AMDChina,關注 AMD 官方微博@AMD中國。

|

AMD、AMD Arrow 標識、Alveo、Virtex、Vivado 及其組合為超威半導體公司的商標。其它名稱僅供參考之用,可能是其各自所有者的商標。 |

|

[1] 截至 2023 年 8 月 16 日,AMD 性能實驗室使用 Vivado? Design Suite 2023.1,對運行在 Vivado Lab(硬件管理器) 2023.1 上的 Alveo UL3524 加速卡進行了測試。基于 GTF 時延基準設計,經(jīng)過配置,可在內部近端回送模式下啟用 GTF 收發(fā)器。GTF TX 和 RX 時鐘在大約 644MHz 的相同頻率下工作,相移為 180 度。GTF 時延基準設計通過鎖存單個空閑運行計數(shù)器的值來測量硬件中的時延。時延即為 TX 數(shù)據(jù)在 GTF 收發(fā)器處鎖存的時間與其在路由回 FPGA 架構之前在 GTF 接收器處鎖存的時間之間的差值。時延測量不包括協(xié)議開銷、協(xié)議幀、可編程邏輯 (PL) 時延、TX PL 接口設置時間、RX PL 接口時鐘輸出、包飛行時間和其它時延來源。基準測試運行了 1,000 次,每次測試 250 幀。引用的測量結果基于 GTF 收發(fā)器"RAW 模式",其中收發(fā)器的物理介質連接子層 (PMA) 將數(shù)據(jù)"按原樣"傳遞到 FPGA 架構。時延測量結果在此配置的所有測試運行中保持一致。系統(tǒng)制造商可能會修改配置,因此產(chǎn)生不同的結果。ALV-10 |

|

[2] 基于 Virtex UltraScale+ GTY 收發(fā)器與超低時延 GTF 收發(fā)器的仿真比較。 |