上海2021年10月27日 /美通社/ -- 世芯電子設計研發副總裁 James Huang 表示,世芯電子將芯粒革命視為摩爾定律極具成本效益的延伸。

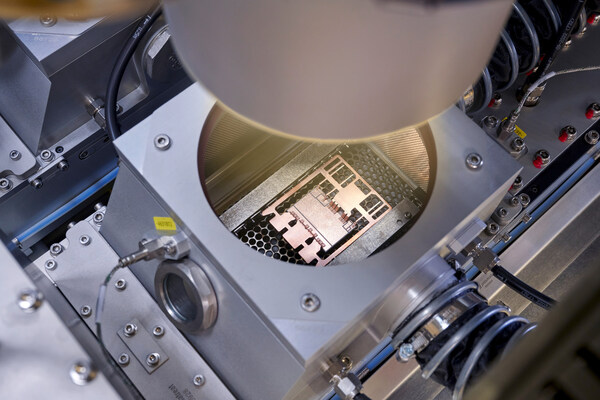

在臺積電 2021 年開放創新平臺的技術演講中,James Huang 強調,芯粒和先進封裝提供了與單片 SoC 相比具有競爭力的成本結構,同時保持了相近的性能和功耗。

James Huang 引用了兩項對芯粒/封裝發展至關重要的技術:一種是臺積電的 3DFabric 和 CoWos® 組合技術。 另一個是世芯的 APLink 芯粒間互聯 I/0。

APLink 芯粒間互聯 I/0 支持多個芯粒之間的高速數據交換。APLink 1.0 的目標是臺積電的 12 納米工藝,而 APLink 2.0 的目標為7納米工藝。5納米工藝的APLink 3.0目前正在進行測試芯片結果評估,已達到目標線速。APLink1.0和2.0的線路速率分別為1Gbps和4Gbps。

超越眼前的視野,James Huang 向與會者展示了未來的高峰。在詳細介紹 APLink 4.0 時,他透露了以 3 納米為目標的芯粒間互聯 IP。

APLink 4.0 的互連將采用以標準內核電壓運行的源同步 I/O 總線。每個 PHY 模塊以 12Tbps 的速度運行,每條 DQ 線路的速度高達 16Gbps,但只有 5 納秒的延遲。這些規格能支持可靠的系統操作。

APlink 4.0 IP 將支持北/南和東/西方向以及對稱的 PHY 布局排列,這最大限度地減少芯粒間互聯的信號線長度。

“真正將未來變為現實的是一種靈活的商業模式,它更符合未來技術創新需求。”James Huang 指出。

在實現多芯粒系統設計時,世芯與客戶的合作模式提供多個起始點,包含產品規格制訂、SoC 設計或系統調試與量產等合作起始點。

如需更多信息,請訪問 www.alchip.com。

關于世芯電子

世芯電子股份有限公司成立于 2003 年,總部設于臺北。提供系統公司高復雜度、高產量 SoC 設計及量產服務。產品的應用市場包含 AI 人工智能、HPC 高速運算、娛樂機臺、手機、通訊設備、計算機及其他消費性電子 IC 產品。世芯致力于為客戶提供最高效益/成本比的解決方案,確保客戶一次投片成功并快速將產品導入市場。世芯成立以來,已完成眾多高階制程(16 納米以下)及高復雜度 SoC 設計的成功案例,并于 2014 年 10 月 28 日于臺灣證券交易所掛牌上市(股票代號:世芯-KY: 3661)。目前在美國(硅谷)、日本(新橫濱)、中國大陸(上海、無錫、合肥、廣州、濟南、深圳)和臺灣(新竹)擁有分部。