應對無線網絡“城市病”

隨著城市人口越來越多、樓房越來越密集,無線網絡也遭受著“城市病”的困擾,無線網絡速率在人口密集地區一直不如人意。加上4G的迅速普及以及智能手環等各種可穿戴產品不斷上市,就對無線網絡提出了更高的要求,也直接給基站帶來壓力。

作為基站的“大腦”,通信處理器一直備受關注,也是“兵家必爭之地”。對于其發展趨勢,普遍的觀點是:高性能異構SoC將進一步發展,每個廠商將基于現有架構,配置性能更高的核,并且會采用多核DSP+多核CPU或者多核DSP+多核ARM。此外,還會集成更多的模擬部分,當然低功耗也是必不可少的,這種趨勢也正是為了適應無線基礎設施的發展需求。基站經歷從模擬到數字、從窄帶到寬帶的發展歷程,每4~5年就更新一代,但其發展方向一直沒有改變,都是向高性能、高可靠、布網靈活、升級維護方便、節省全生命周期成本的方向發展。目前為了解決覆蓋和容量問題,小基站如雨后春筍一般的迅速發展,因為數據傳輸速率越大,無線覆蓋就越受到挑戰,小基站也就更合適。需要指出的是,小基站不是只指四代,而是針對大規模的4G、3G以及GSM的支持上,它更多是用于熱點的覆蓋,包括大的社區、商場、辦公樓以及校園網的覆蓋。

為小基站而生的4核異構SoC

飛思卡爾三年前推出業界首款面向各種基站的多模無線基站處理器系列,便引領片上基站市場。飛思卡爾城域小區解決方案面向高帶寬、低功耗的基帶應用,并針對LTE (FDD和TDD)及WCDMA (HSPA+)城域基站應用進行了優化。今年2月推出的QorIQ Qonverge B3421 SoC面向快速增長的城市板塊,鞏固了飛思卡爾在無線網絡領域的領導地位。

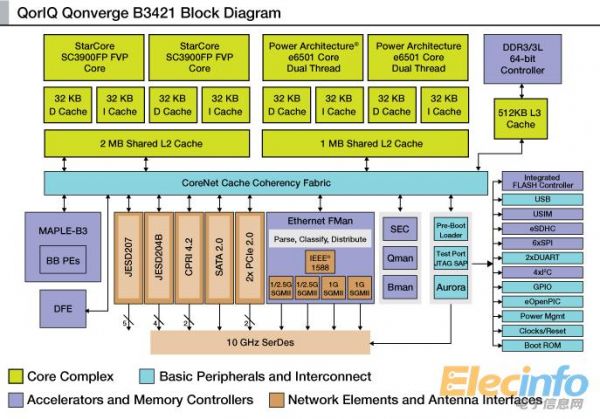

QorIQ Qonverge B3421無線基礎架構片上系統基于先進的SoC架構,采用28 nm工藝技術制造,集成有數字前端(DFE),是一款高性能基帶解決方案,適用于對功耗、尺寸和成本要求較為嚴格的小型小區部署。該器件就是采用雙核DSP+雙核CPU的異構形式,配備兩個基于Power Architecture?技術的雙線程64位e6501內核(帶有AltiVec SIMD引擎)、兩個基于StarCore技術的SC3900FP定點/浮點DSP內核,以及針對特定應用的加速器,具有卓越的處理性能,可在上行鏈路和下行鏈路都保持高數據吞吐量的同時,實現功耗最優化。B3421已為在LTE和Wi-Fi下運行進行了全面優化,適合采用FDD-LTE、TDD-LTE和LTE-Advanced協議的企業微微小區、戶外微微小區和城域小區等小型小區基站。B3421內部架構如圖1所示。

圖1 QorIQ Qonverge B3421內部架構

從圖1可以看到,貫穿在各核心部件中的是CoreNet,它是內部無阻塞緩存一致性交換結構,可以保持SoC中CPU、DSP、DDR3、MAPLE-B3等各核心部件數據交換暢通無阻,其每簇原始帶寬高達42.5 GB/s。很多工程師常常抱怨多核處理器特別是異構多核SoC給他們的編程帶來很多不便,難度太大。CoreNet配上可加快產品上市并優化性能的商業級VortiQa 第1層基帶軟件以及經過現場驗證的層1/物理層(PHY),降低了異構多核帶來的軟件開發難度。